Mail:info@anke-pcb.com

Whatatp / Weckat: 008618589033832

Skype: SannyduAnbsp

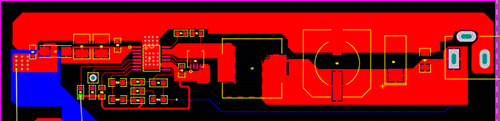

Tres facies ut secure potentia integritas inPCB designing

In modern electronic consilio potentia integritas est necessaria pars PCB consilio. Ut firmum operationem et perficientur electronic cogitationes, considerandum et consilio comprehendendo a potentia fons ad recipiens.

Per diligenter designing et optimizing potentia modulorum, interiore iacuit plana, et potentia copia eu potest vere consequi potestate integritas. Hoc articulus erit dellvit in his tribus clavem facies providere practica ductu et strategies pro PCB designers.

I. Power Module layout Wiring

Potestas moduli est industria fontem omnis electronic cogitationes, eius perficientur et layout directe afficiunt firmitatem et efficientiam totius ratio. Rectam layout et fuso non solum redigendum strepitus intercessiones sed etiam ut lenis current fluxus, ita improving altiore perficientur.

2.power moduli layout

1.Source Processing:

Power moduli sit solvit specialis operam cum servit ut principium punctum potentiae. Reducere sonitus introductio, elit circa virtute moduli debet custodiri ut mundum fieri potest ad adjacency aliisaltusaut strepitu, sensitivo components.

2.Close ad potentia copia chip:

Power moduli poni proxime virtutem chip quam. Hoc potest reducere damna in hodiernam tradenda processus et reducere in area requisitis interiore layer planum.

3.Heat dissipatio considerations:

Power moduli potest generate calor per operationem, ut ita sit, ut non sunt obstantia super illud calor dissipationem. Si necesse, heatsinks aut fans potest addidit ad refrigerationem.

4.avoiding ansas:

Cum fuso, vitare formatam current ansas ad redigendum facultatem electro intercessiones.

II. Interiorem iacuit planum consilium planning

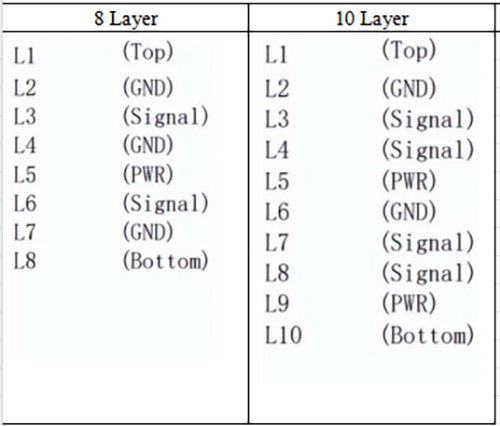

A. Layer Stack Design

In PCB EMC Design, Layer ACERVUS Design est a key elementum, quod necessitates ad considerandum fusum et potestatem distribution.

A. Ut humilis impedire characteres virtutis planum et absorbet terra sonitus cooplentia, distantia inter virtutem et terram planis non excedat 10mil, typice suadetur minus 5mil.

b. Si una potentia planum non potest implemented, superficiem accumsan potest ad ponere de potestate planum. Et propinqua adjacent potestate et terram planis formare planum Capacitor cum minimum ac Impedance et optimum summus frequency characteres.

c. Vitare adjacent duo potestatem stratis, praesertim cum magna intentione differentias, ne sonitus coitus. Si necessaria, crescere spacing inter duas potestatem layers quantum fieri potest.

d. Reference plana, praesertim referat plana, debet ponere humilis impedire propria et optimized per bypass capacitors et iacuit referendo.

B.Multiple Power Segmentation

A. Nam specifica parva-range potestatem fontes, ut core opus voltage cuiusdam IC chip, aeris debuit ponere signo accumsan integritas virtutis planum ad redigendum rotundum.

b. Selectio sercentis latitudine oportet. Cum voltage maior quam 12V, latitudo 20-30mil esse; Alioquin eligere 12-20mil. Quod semestia latitudine inter Analog et digital potestatem fontes indiget augeri ne digital potestate a intercedente cum Analog potestate.

c. Simple potestatem networks perficitur in fuso accumsan, et diutius potestatem networks debet habere filter capacitors addidit.

d. Segmented potestas planum debet regulari ne irregulares figuris causando resonatur et augeri impedirentance. Dum angusta denudat et dumbbell informibus divisions non licet.

c.plane filtering

A. Plane planum propius copulata terram planum.

b. Nam eu cum operating frequencies excedens 500mhz, praesertim confidunt in plano capacitor filtering et uti compositum de capacitor filtering. Et filtering effectus indiget confirmari per virtutem integritas simulation.

c. Install Inductors ad decoupling capacitors in potestate planum, ut videantur capacitor ducit et augendae capacitor vias ut potentia terra impeditance est inferior quam in scopum impedimentis.

III. Power chip layout wiring

Quod potentia chip est core electronic cogitationes, et ensuring eius potentia integritas est crucial pro meliorem fabrica perficientur et stabilitatem. Power integritas imperium in potestate eu maxime involvit fuso pertractatio de chip potentia paxillos et rectam layout et wiring de decoupling capacitors. In his autem detail considerations et practica consilio de his facies.

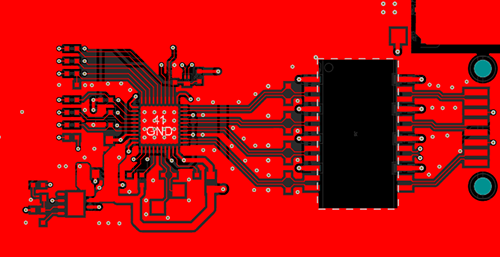

A.Chip Power Pin fuso

Et fuso de chip potentia paxillos est a crucial parte potentia integritas imperium. Providere firmum vena copia, commendatur ad pulmentarii et fuso potentia paxillos, fere ad eadem latitudine ut chip paxillos. Typically, inMinimum widthMinus quam 8mil, sed melius consequi ad consequi latitudinem 10mil. Per augendae fuso width, impediat reduci, ita reducendo potestas sonitus et curam sufficientem copiam ad chip.

B.layout et fuso decoupling capacitors

Decoupling capacitors ludere a significant munus in potentia integritas imperium ad potestatem eu. Secundum capacitores et applicationem requisitis, decoupling capacitors plerumque dividitur in magna et parva capacitors.

A. Magna Capacitors: magna capacitors plerumque aequaliter distribuit circa chip. Ex inferioribus resonant frequency et maior filtering radii possunt efficaciter filter de humili frequency sonitus providere firmum potestate copia.

b. Capacitors parva: parva capacitors habent altiorem resonantem frequency et minor filtering radius, ita ut proxime ad chip paxillos. Ponebantque longius non efficaciter filter de altus frequentia sonitus amissis decoupling effectus. Rectam layout ensures efficaciam parva capacitors in filtering summus frequency sonitus plene adhiberi.

C.Wiring modum parallel decoupling capacitors

Ad amplius amplio potentia integritas, multiple decoupling capacitors sunt saepe connectitur in parallel. Pelagus propositum huius praxi est ad redigendum est equivalent series inductance (esl) de singulis capacitoribus per parallel coniunctionem.

Cum paralleling multiple decoupling capacitors, attentionem solvit ad collocatione Vias pro capacitoribus. A communi usu est ut offset in vias virtutem et terram. Pelagus ad redigendum mutua inductance inter decoupling capacitors. Ut mutua inductance est multo minor quam ESL unius capacitor, ut altiore ESL IMPEDIUM post parallendo plures decoupling Capacitors est I / n. Per reducendo mutua inductance, filtering efficientiam potest efficaciter aucta, cursus melius potestate stabilitatem.

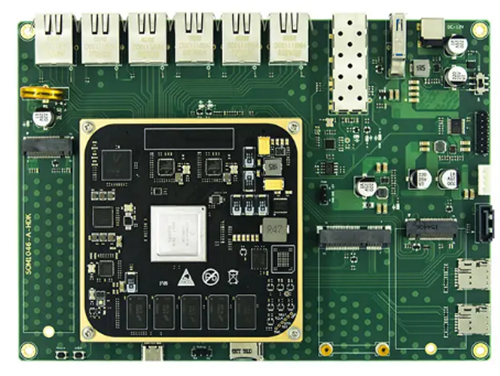

LayoutEt fuso virtutis modulorum, interiorem stratum planum consilium planning, et recte tractantem virtutis chip layout et wiring sunt necessaria in electronic fabrica consilio. Per propriis layout et fuso, possumus curare stabilitatem et efficientiam potentiae modules, redigendum strepitus intercessiones et amplio altiore perficientur. Layer ACERVUS Design et multiple potestatem justo amplius optimize characteres potentia plana, reducendo potentia strepitus intercessiones. Propriis pertractatio virtutis chip layout et wiring et decoupling capacitors sunt crucial ad imperium integritas imperium, cursus stabile current copia et effective sonitus filtering, enhancing et efficax et stabilitatem.

In practical operantes, variis factoribus ut current magnitudine, fuso width, numero vias, coupling effectus, etc., opus est comprehenditur considerari ad rationalem layout et fuso decisions. Sequere Design Specifications et optimum exercitia ut imperium et optimization potentia integritas. Tantum hoc modo possumus praebere firmum et efficient potestas copia electronic cogitationes, occursum ad augendae perficientur postulat, et expellam in progressionem et progressus electronic technology.

Shenzhen Anke PCB Co., Ltd

Post tempus: Mar-25-2024